Hardware & Software Designs for Secure IoT

IoTデバイス上の個人情報や知的財産を狙うサイドチャネル攻撃やマルウェアに対して,攻撃の検出,情報の保護や攻撃されにくいハードウェア・ソフトウェアの新たな設計手法を研究しています.

Next-Generation Neural Networks

組込みシステムに搭載可能な簡素で高速なニューラルネットワークの演算モデルを探索し,低消費エネルギーな次世代アーキテクチャの構築・設計技術を研究しています.

Ultra-Small, Low-Power Processors for IoT

プロセッサ単体の機能を極限まで削減した超小型・低消費電力プロセッサを開発しています.既存の組込みプロセッサに比べ,電力効率・エネルギー効率を大幅に改善できます.

Many Others

What's New

本研究室の代表である原は,2025年11月1日付けでフランスの国立研究所CNRSへ異動しました.そのため,本研究室では新しいメンバーの受け入れはできません.フランスの「博士課程」に進みたい方は原まで連絡をしてください(※日本のような修士課程や研究生制度はありません).

The PI of this research group, HARA, has moved to the CNRS in France as of November 1st, 2025. Therefore,…

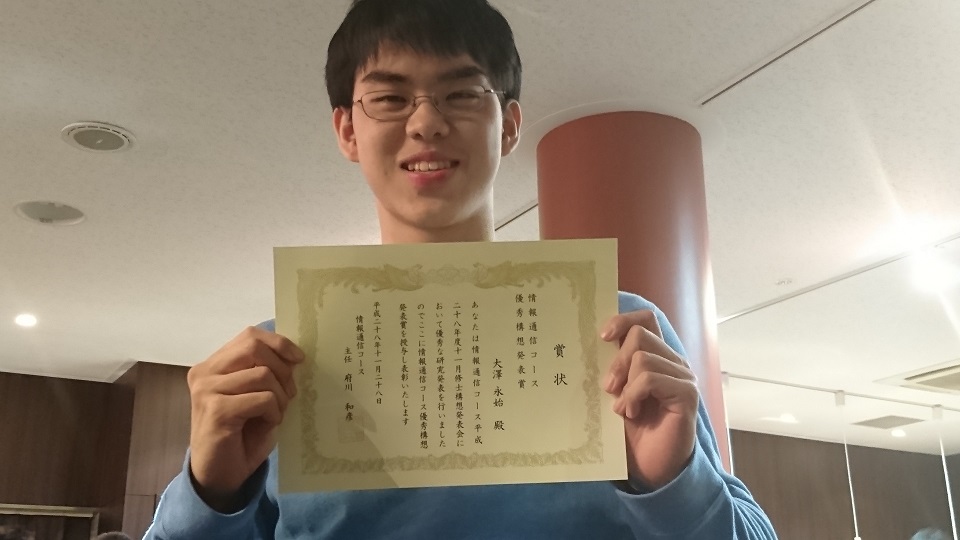

修士1年の森下さんの論文"HCLL-Lock :機能攻撃への高い耐性を持つハードウェアIP保護手法"が,情報処理学会コンピュータセキュリティ研究会にて学生論文賞を受賞しました.おめでとうございます!

博士課程のZengさんの論文"Lightweight Real-Time Detection of DDoS Attacks on IoT Devices via Power Side-Channel Analysis"が,国際会議IEEE International Conference on Communications (ICC)に採択されました.

修士1年の一岡さんの論文"PreLock: Precision Locking for Protecting Embedded Processor"が,国際会議Asian Hardware Oriented Security and Trust Symposium (AsianHOST 2024)に採択されました.

2023年度修士卒の永松さんの論文"Mixed-precision Neural Architecture Search and Dynamic Split Point Selection for Split Computing"が,国際論文誌IEEE Accessに採択されました.

Contact info

所属 東京科学大学 工学院情報通信系

所在地 東京科学大学 大岡山キャンパス

教員室 南3号館 317号室

学生室 南3号館 314, 315, 316号室

問い合わせは hara[at]cad.ict.e.titech.ac.jp まで.

E-mail to hara[at]cad.ict.e.titech.ac.jp for your inquiry

佐宗君の受賞@M1構想発表会。おめでとうございます!