Our Research

デスクトップコンピュータやノートパソコンのようにどんなソフトウェアでも動かせる計算機システムとは異なり,携帯電話,デジタルテレビ・電子レンジ等の家電製品,自動車・航空機・衛星等のように特定の処理を行う計算機システムを 組込みシステム (Embedded System) と言います.組込みシステムは,それぞれの機器にとって効率の良い処理をできるようにカスタマイズされたプロセッサ・専用回路,メモリ等から成り,それらの部品を製造コスト・性能・エネルギー・寿命等の観点から最適に設計することが求められています.モノのインターネット (Internet-of-Things; IoT) のシステムでは,従来の組込システムの制約が更に厳しくなっています.原研究室では,これらのニーズに応じて組込み/IoTシステムを最適・自動設計する技術を,ハードウェア・ソフトウェアの両面から広く研究しています.

IoT時代に考える組込みシステムのセキュアな設計手法

Secure Embedded Systems Designs in IoT

|

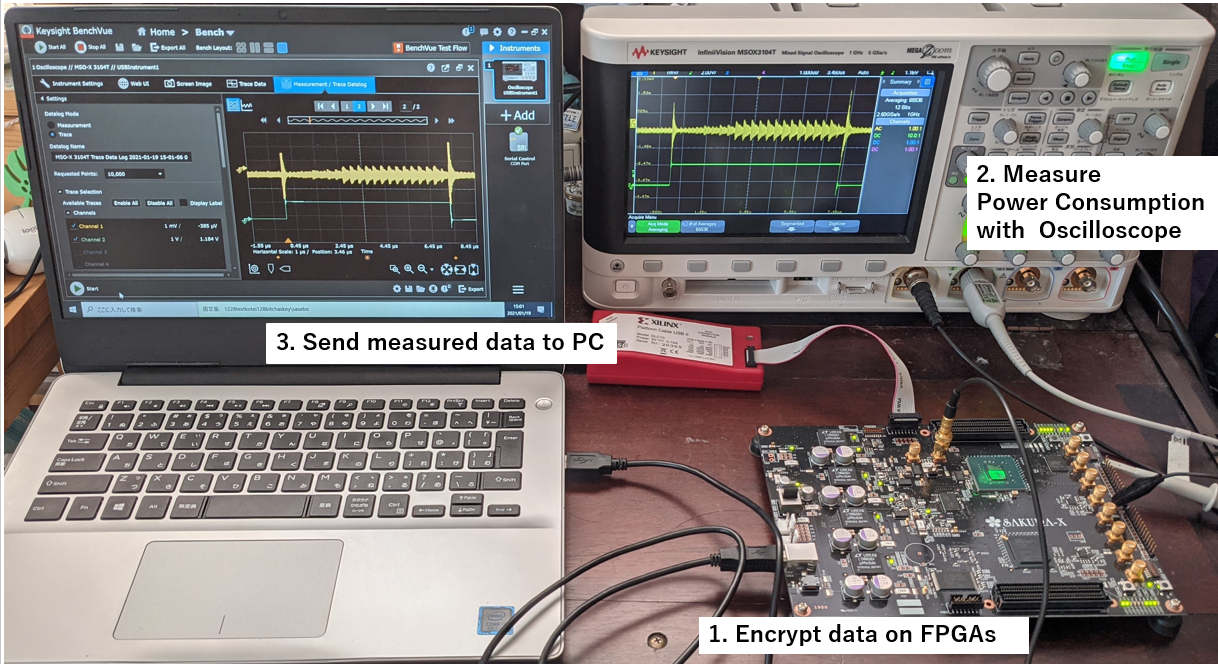

IoT時代に個人情報や知的財産を保護するためには,IoTデバイスからの情報漏洩やマルウェアによる攻撃への対策を講じる必要があります.本研究室では,IoTデバイスのセキュリティについて,主に3つの観点から研究をしています.①IoTデバイスから漏れ出る電力を解析することで暗号システムを破る攻撃の脅威が高まっています.漏洩を防ぐハードウェア(プロセッサや暗号専用回路)とソフトウェアの新たなセキュア設計手法の確立を目指します.②ハードウェア設計知財 (IP) が不正に流出し,悪用される被害が増加しています.IPを不正利用されない設計方法や,正規品であることを確認できる仕組みを研究開発しています.③高度な秘密計算を行うために必要な乱数を効率的に共有するアーキテクチャを開発しています. ・現在進行中のプロジェクトJST CREST "Trustworthy IoTシステム設計基盤の構築" JSPS 基盤(B) "スケーラブルかつセキュアな組込みハードウェア設計技術の基盤構築" JSPS 二国間交流事業共同研究 (FWO/JSPS) "組込みシステムセキュリティの保護と解析" ・共同研究電気通信大学 崎山教授,李准教授 Dr. Nikova, Katholieke Universiteit Leuven, Belgium |

電力解析攻撃への対策を講じた暗号専用回路の評価 |

次世代IoTニューラルネットワークの設計・探索

Next-Generation IoT Neural Network Designs and Exploration

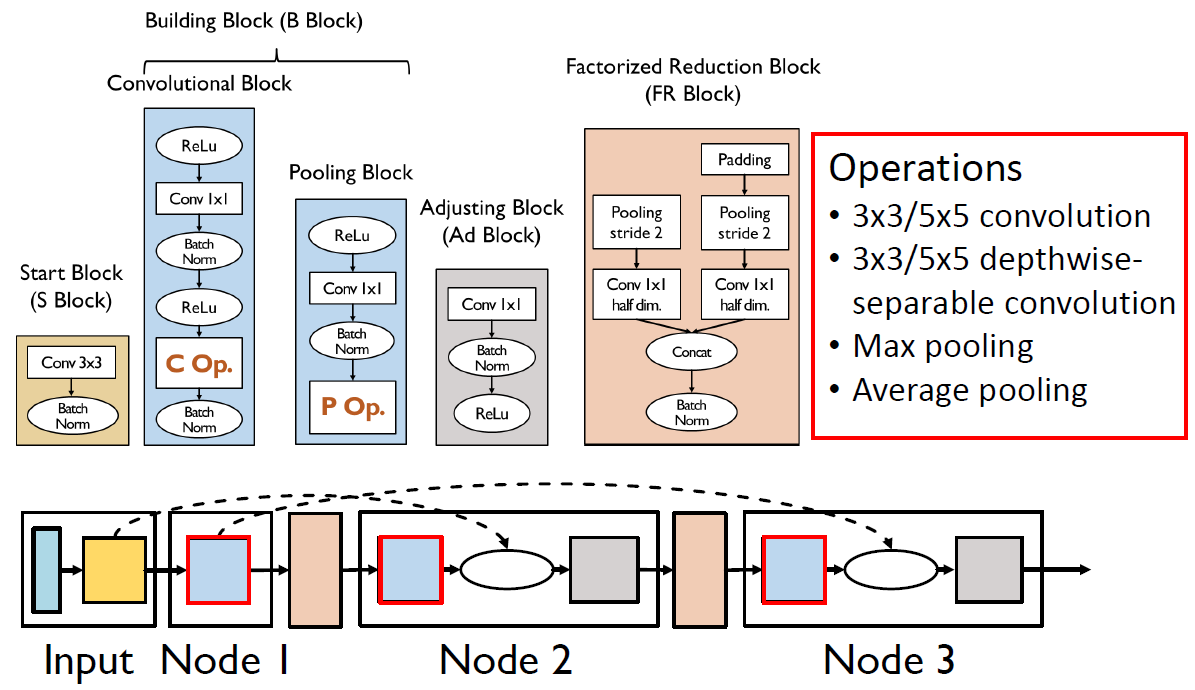

| 近年は,様々な方法でソフトウェア(アプリケーション)を処理する計算機システム(アーキテクチャ)があり,それらに対して,ニューラルネットワーク向けアーキテクチャ・ソフトウェアの協調開発に取り組んでいます.現在取り組んでいる課題は,以下のように多岐に渡ります.①汎用計算機(CPUやGPGPU)向けに設計されたニューラルネットワークを,資源制約の厳しい組込みシステム上にそのまま持ってきても,処理・エネルギー効率が悪く,実用化できません.高い精度を維持しつつ,組込みシステム向けの軽量なモデルを効率的に探索することで,IoTデバイスのAI化を加速します(右図).②プライバシーを考慮した分散機械学習の学習方法や推論方法を確立し,利用者のプライバシー保護が実現できるようになります.③ネットワークからのサイバー攻撃やトロイなどのマルウェアによる不正なシステム侵入を検出する機械学習モデルを構築し,サイバーセキュリティの改善を目指します.

これらの研究は,組込みシステム向けGPGPU(Jetson等),FPGA(再構成可能デバイス),マイコン等を対象に,ハードウェア(アーキテクチャ)・ソフトウェア(アプリケーション)の両面から幅広く研究・開発を行っています. ・現在進行中のプロジェクトJSPS 基盤(A) "モビリティ革新に向けた大規模点群のリアルタイム推論のための分散機械学習理論と基盤" JSPS 国際共同研究加速基金(海外連携研究)"リサイクル半導体を活用したサステイナブルかつセキュアIoTプラットフォームの構築" ・共同研究Prof. Mühlberg, Université libre de Bruxelles, Belgium 東京科学大学 西尾准教授 |

組込みシステム向けに,高精度かつ軽量なニューラルネットワークを探索する技術 |

IoTを加速するエッジコンピューティング向けプロセッサ

Microprocessor Designs towards Edge Computing in Internet of Things (IoT)

|

エッジデバイス(クラウドの外にあり,我々の生活により身近なデバイス)上でデータを効率良く管理・処理することで,モノのインターネット(Internet-of-Things; IoT)技術の高度化・普及を更に加速し,我々の生活をより安全・豊かにすることができます.これまでのコンピュータアーキテクチャは,多様化するアプリケーションを網羅できるように多機能化し,機能や複雑さ(製造コスト)が膨れがってきています.本研究室では,新たなIoT技術を牽引するエッジコンピューティング向けのアーキテクチャが持つべき機能を再考し,複雑さを抑えられる設計手法に取り組み,超小型・省エネで画期的なアーキテクチャの研究・開発を行っています.コンピュータアーキテクチャ(ハードウェア設計)と,そのメリットを最大化するソフトウェア開発の両面からアプローチしています. 軽量な処理から成るヘルスケアやファクトリーオートメーション等のモニタリングを対象に,応用展開していきます. ・研究成果東京工業大学/JST プレスリリース, "エッジ端末に適した小型省電力プロセッサを実証 従来比3.8倍のエネルギー効率でヘルスケアIoTに道," 2021年2月19日. |